从POCI协议层探索 UtilityNet 的核心价值潜力

5月28日,UtilityNet 官方在其Medium发布《Exploring the Core Value Potential of UtilityNet from the POCI Protocol Layer》,下文为中文翻译版:

本篇文章主要内容框架如下,可参考阅读:

软件开发的历史发展

传统「硬件定义软件」的发展局限

UtilityNet 的逆向工程——软件定义硬件/芯片的优势

为什么说UtilityNet价值的核心是始于协议?

芯片就是算力的核心

芯片级安全:P一致性 / Portion Consistency

POCI / 可信计算完整性证明

UtilityNet算力留存流转的实现与优化

差异化:闲置算力 VS 有效算力

不同共识机制的表现对比

总结:构建开源、共享的分布式算力生态

软件开发的历史发展

20世纪60年代

软件工程被认可为一种独立的工程形式,但同时也是软件开发陷入困境的时期。软件方面难以跟上硬件的步伐,这给该领域带来了问题。

20世纪70年代

软件危机仍在继续,而软件工程师们则试图扭转局面。20 世纪 70 年代,随着新理念、新语言和新硬件的推出,软件工程开始崛起。

20世纪80年代

随着软件危机逐渐消退,该阶段继续发生了巨大的变化。新的语言和工具帮助开启了更好的工程之旅,并开始了面向对象编程的转变。

20世纪90年代

这十年是编程语言繁荣的十年,如今最流行的一些编程语言都诞生了。软件工程行业还发生了许多其他重大变化:面向对象编程开始流行,互联网首次出现,并引入了一种新的开发方法。

进入21世纪

随着公司继续改进二十年前建立的体系,语言和工具不再是关注的焦点。开发人员更加关注方法论,因为他们希望让流程更能满足客户需求、更有利可图、更易于创建。

2010年代

在不断改进语言和方法的同时,重点再次转移到满足软件工程师的需求,以新的学习方式来加强传统的软件工程教育。

2020 年代

人工智能(AI)和机器学习(ML)在2020年代成为软件开发中的重要力量。2020年代的软件工程正由这些趋势所塑造。

传统「硬件定义软件」的发展局限

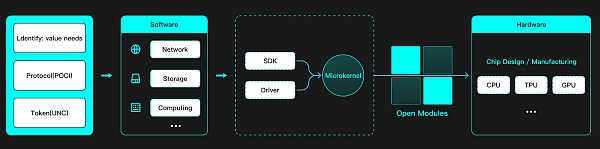

在几十年软件开发形成的历史中,开发者始终遵循「硬件定义软件」hardware-defined software (HDS) 的底层逻辑,即硬件定义了驱动,驱动定义了系统接口,然后基于这些接口开发软件SDK,最终创造出软件。这一过程要求开发者在既定的硬件体系和平台内尽可能地创造价值。

通过下方,我们可以更清晰地了解到传统HDS模式发展的局限性:

专用硬件的局限性:在计算机时代,许多软件程序是为特定的硬件平台编写,限制了软件的可移植性和可重用性。例如,IBM的大型机软件通常不能在其他品牌的硬件上运行。

性能瓶颈:在某些情况下,软件的性能受到硬件性能的限制。例如,早期的图形处理软件由于图形处理单元(GPU)的性能限制,无法实现复杂的视觉效果。

创新受限:在移动设备领域,由于硬件的多样性和碎片化,开发者需要为不同的硬件配置编写不同的代码,这限制了他们开发跨平台应用的能力。

成本和资源:开发专用硬件通常需要大量的投资和时间,这使得小型企业和初创公司难以承担,限制了他们在软件开发上的创新能力。

技术过时:技术的快速发展,专用硬件可能很快变得过时,而软件更新通常需要等待新的硬件支持,这导致软件功能无法及时更新以满足用户需求。

在如今AI人工智能的催化下,软件和硬件都在不同程度的更新迭代,很显然,两者的发展和创新显得捉襟见肘,软件的发展渐缓又很大程度上受制于硬件/芯片的局限。从而导致软件开发者受制于由硬件定义的系统编程,开发者不能够天马行空的去创新,限制了开发者的想象力。

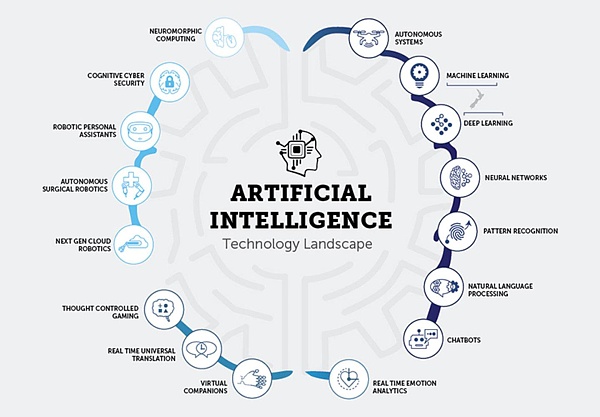

-AI人工智能生态-

UtilityNet 的逆向工程——软件定义硬件/芯片的优势

UtilityNet,是一个去中心化数字芯片网络,旨在为下一代边缘计算和人工智能基础设施提供芯片资源。Utility的定义,是来源于各种类型的芯片,Net的定义是来源于去中心化的网络。

而UtilityNet 是一个从价值需求本身颠覆了传统的硬件先行的逻辑。

Software Defined Hardware (SDH)软件定义硬件/芯片 ,SDH的概念旨在打破硬件定义软件(Hardware-Defined Software, HDS)的传统模式,让硬件更加灵活,以适应不断变化的软件需求。SDH 通过创建可运行时重新配置的硬件和软件,使得硬件能够根据软件的需求进行调整,从而释放开发者的创新潜力。

在这里我们把UtilityNet称为一个软件,采用Software Defined Hardware (SDH)的方法。在这种方法中,价值创造的过程始于一个有价值的代币及其背后的协议。由有需求价值的代币和协议定义了软件,然后软件定义了所需的SDK,接着是驱动,最终影响到物理芯片的设计。UtilityNet SDH的目标是构建运行时可重新配置的硬件和软件,在不牺牲数据密集型算法的可编程性的情况下实现接近 ASIC 的性能,而不会产生与 ASIC 相关的成本、开发时间或单一应用程序限制。

这种由软件到硬件的逆向工程的过程在区块链历史上从来没有发生过,而这才是UtilityNet价值驱动的核心逻辑。

为什么说UtilityNet价值的核心是始于协议?

UtilityNet的价值核心始于协议,即POCI/可信计算完整性的证明,因为从协议本身就决定了为用户最大限度提供每个设备的有效算力。它确立了算力贡献和验证的基础,而UNC代币则是在此基础上,对用户贡献的算力进行奖励和价值交换的媒介。POCI 不再依赖于持续的计算任务来维持网络,而是通过芯片内部的安全引擎模块结合链上加密学原理,让芯片能够自我证明其算力,在减少算力损耗和促进算力流转方面表现出独有的创新实践。

这也是UtilityNet价值核心始于POCI 协议,这区别于绝大多数同类型项目。

芯片就是算力的核心

那么协议定义的硬件,可以多种多样,为什么从理论上来说需要定义到芯片这么底层呢,这个是因为非准入的区块链和准入的有本质区别,并且和tokenized centralized web3 project有截然不同的加密学要求。

一张成熟量产的芯片,往往有一个公认的算力计量标准。那么,从共享经济的角度来说,只要能在用户贡献算力的过程中,通过链上验证用户在线贡献的硬件芯片的真实性以及在线状态,理论上就可以认为用户为平台贡献了该芯片对应的算力值,就可以给予用户相应的代币奖励。这时,该芯片的算力就能被冗余下来以备随时租给真正的算力需求方,而算力需求方则可以通过去二级市场或者场外购买相关代币去租到自己想要的算力。

通过这种方式,就能够真正的让有价值的 AI 算力在激励层的作用下流转到需要它们的客户手里,而不是被矿工们为了获取代币激励而被迫做无效计算去浪费掉。甚至还有部分项目,从协议机制或者技术角度来说,根本实现不了有效算力的留存和再次流转。

芯片安全:P一致性 / Portion Consistency

-电子显微镜下的3D芯片-

首先我们来看 Portion Consistency, 什么是P一致性,芯片的生产制造有个特点,是它是由光刻的工艺制作,从掩膜投射EUV在涂了光刻胶的晶圆上一层一层蚀刻,我们看它的横截面它是3d结构,这也就意味着我们想更改一个集成电路成品的哪怕一个晶体管都是不可能的,所以,IC的一部分和整体具有着一致性安全,这个对于使用芯片物理地证明和加密学去定义整个证明过程是至关重要的,我们能够通过证明量产芯片的局部单元去证明整个集成电路存在。

它定义了一个物理的能力是如何被大众公允的,通过芯片的IC和benchmark测试,从而让一个物理的芯片具有了能力的认证。

POCI / 可信计算完整性证明

可信计算完整性的证明(Proof of Computing Integrity)现在我们来看 PoCI的实现逻辑,通过约定芯片中一个Portion的能力和设计,来证明芯片本身,然后通过计算能力传导来证明计算能力。

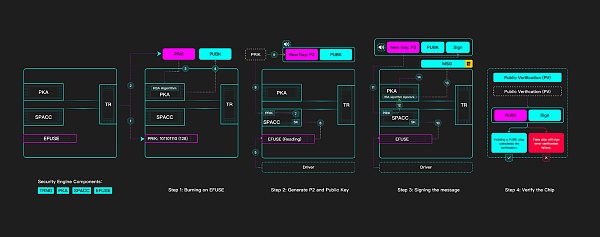

UtlityNet 芯片安全引擎 (SE)的组成主要包含四个部分: TRNG、PKA、SPACC、EFUSE。

POCI(Proof of Computational Integrity)芯片验证逻辑

Step-1:在 EFUSE上刻录

TRNG(真随机数发生器)生成一个 128 位的随机数 N

N 将以二进制形式存储在一个名为 EFUSE 的特定区域。通过高压烧毁电路的某些部分,将其标记为 “1”。那些 “0 ”区域保持不变。现在,我们将 N 密匙称为 SK,因为除非芯片驱动程序驱动读取,否则在纳米级区域通常是无法读取。

Step-2:生成 P2 和公钥

驱动程序将控制 TRNG 生成另一个随机数,将其作为私钥 (PRIK)。PRIK 将通过 PKA 模块,根据 RSA 算法生成公钥 (PUBK)。

然后,驱动程序将激活 EFUSE 的读取,获得 SK,SK 将被送入 SPACC 模块,PRIK 也将被送入 SPACC 模块。在 AES 加密算法下,PRIK 会被 SK 加密,生成一个名为 P2 的新密钥。

P2 和 PUBK 将被公开,PRIK 将被丢弃,不留任何痕迹。

Step-3:签署信息

P2 将被发送到 SPACC 模型,驱动程序将读取 EFUSE,获得 SK。有了 SK,它就会将 P2 解密为 PRIK。

消息摘要将被发送到 PKA 模块,PRIK 也将被发送到 PKA 模块,使用 RSA 算法,PRIK 将对摘要 Msg 进行签名,并生成签名 Sign。签名将被公布。

Step-4:验证

任何人都可以手持 Sign 和 PUBK 进行验证。利用 RSA 算法提供的函数 V(Sign,PUBK),可以测试签名。如果 V = true,则表示签名是由持有 PUBK 的芯片完成的。如果为假,则表示签名错误,即持有的芯片是假的或错误的。任何挑战者都可以挑战芯片的存在真实性,但是全世界只有这张芯片本体能够使用数字签名证明自己。

这也就是为什么 UtlityNet叫做数字芯片网络的原因,它是一种去中心化 RWA(Real World Assets)。

UtilityNet算力留存流转的实现与优化

那么UtilityNet是如何实现有效的降低算力损耗,实现有效算力留存和再次流转的?

差异化:闲置算力 VS 有效算力

UtilityNet提出的POCI机制通过确保计算任务的有效性和精确性,旨在减少验证和挖矿等过程中的算力消耗,降低无效计算,不仅减少算力损耗,而且通过鼓励用户提供高质量的算力,增加算力的留存和有效流转。而大多数项目根本就无法把参与激励的这些设备的算力真正的冗余起来,再流转或者出租给其它需要算力的客户。换句话说,项目本身在挖矿的过程中已经把所有参与设备的大部分算力消耗掉了,就不可能把算力再转租给别人。更致命的是,这些项目指定的计算任务都是一些不断重复的垃圾计算任务,并不会对人类社会起到进步和推进作用。

不同共识机制的表现对比

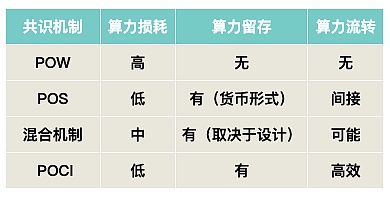

在对比UtilityNet的POCI共识机制与POW、POS以及其他混合机制时,我们可以从算力损耗、算力留存和算力流转等方面进行分析,不同共识机制在算力损耗、留存、流转方面的表现对比:

说明:

算力损耗:表示在共识过程中用于维护网络安全和验证交易的计算资源消耗程度。

算力留存:表示在共识过程中,算力是否能够被保留下来,用于其他目的或未来的使用。

算力流转:表示算力是否能够在网络中被转移或出租给其他需要的参与者。

UtilityNet的POCI共识机制在算力损耗方面具有明显优势,避免了无效计算。在算力留存和流转方面,POCI提供了一种创新的方法,允许算力作为一种可验证和可交易的资源,从而更有效地服务于需要它们的客户。相比之下,传统的POW和POS机制在算力损耗和流转方面存在一定的局限性,而混合机制(例如solana的Proof of Stake, PoS)虽然尝试平衡这些因素,但可能无法像POCI那样直接和高效地解决这些问题。

算力贡献和验证:确立了算力贡献的基础,UNC代币作为奖励和价值交换的媒介。

减少算力损耗:通过芯片内部的安全引擎模块和链上加密学原理,芯片自我证明算力,减少无效计算。

这也就是UtilityNet为何基于POCI机制建立layer1算力网络的初衷!

总结:构建开源、共享的分布式算力生态

本篇我们清晰了解了软件的发展历程,在AI的推动下,软件的创新和发展受制于传统硬件的局限性,要从根本上改变这一切,打破中心化的(无论是软件还是硬件)传统底层逻辑是必要的。

从算力服务生态价值需求出发,UtilityNet 使用POCI 可信计算证明机制,从底层实现高性价比的算力服务,而且拥有更高的芯片级安全,为当下AI发展提供更高性价比的芯片算力基础服务,从而构建一个开源、共享的分布式算力生态。

从UtilityNet 分布式算力生态来看,UtilityNet 提出的SDH/软件定义硬件/芯片,为了公平透明的给每一个贡献算力资源的用户激励,UtilityNet 使用芯片级验证,并依据芯片算力贡献值来正相关分配激励,从而激励芯片的全球范围普及,推动分布式芯片网络的快速构建。从长远的发展来看,具有很高的可行性。

来源:金色财经

交易商排行

更多- 监管中EXNESS10-15年 | 英国监管 | 塞浦路斯监管 | 南非监管92.42

- 监管中FXTM 富拓10-15年 |塞浦路斯监管 | 英国监管 | 毛里求斯监管88.26

- 监管中axi15-20年 | 澳大利亚监管 | 英国监管 | 新西兰监管82.80

- 监管中GoldenGroup高地集团澳大利亚| 5-10年85.87

- 监管中Moneta Markets亿汇澳大利亚| 2-5年| 零售外汇牌照80.52

- 监管中GTCFX10-15年 | 阿联酋监管 | 毛里求斯监管 | 瓦努阿图监管69.35

- 监管中IC Markets10-15年 | 澳大利亚监管 | 塞浦路斯监管91.81

- 监管中金点国际集团 GD International Group澳大利亚| 1-2年86.64

- 监管中VSTAR塞浦路斯监管| 直通牌照(STP)80.00

- 监管中CPT Markets Limited5-10年 | 英国监管 | 伯利兹监管91.56